China's Yangtze Memory Technologies (YMTC) continues to suffer from low yield rates for 128-layer 3D NAND flash manufacturing, which are estimated at only 30-40%, according to market sources.

YMTC started processing wafers using its in-house developed 128-layer 3D NAND process technology at the end of the second quarter, but the process' yield rates have been disappointing, said the sources.

YMTC is also likely to fail to reach its goal set internally of scaling up production capacity to 100,000 wafers monthly by the end of 2021, which may not materialize until the second half of next year, as a result of lower-than-expected yield rates for its 128-layer 3D NAND flash process technology, the sources indicated.

Improving YMTC's 128-layer 3D NAND flash manufacturing yield rates to satisfactory levels may require at least more than one quarter, said the sources, adding that the chipmaker's production capacity is expected to reach only 80,000-85,000 wafers monthly at the end of 2021.

Nevertheless, YMTC has been growing the ecosystem of its partners thanks to China's push for semiconductor self-sufficiency, the sources noted. Multiple China-based brand vendors have already adopted YMTC's 3D NAND flash in their consumer and SSD products.

YMTC's 128-layer 3D NAND chips are being delivered for validation to China's brand smartphone and notebook vendors, and are expected to be featured in commercial products slated for launch in 2022, the sources said. The chipmaker is also looking to tap into the datacenter and server field by breaking into the supply chain of China-based cloud service providers, the sources added.

YMTC could expand its global market share to 7-10% once its monthly capacity scales up to 100,000 wafers, according to the sources.

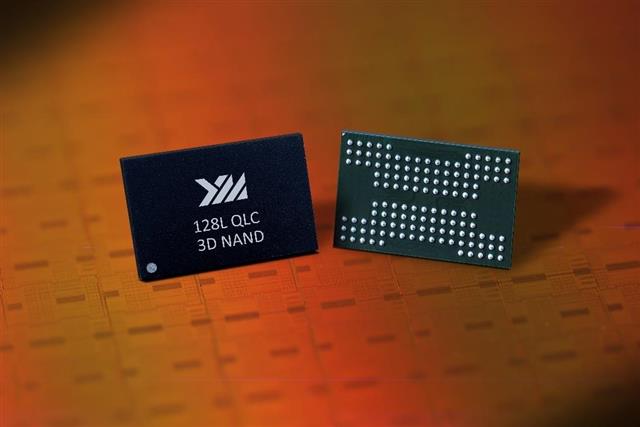

YMTC introduced in October 2017 its in-house developed Xtacking chip architecture for the manufacture of 3D NAND flash memory, and kicked off volume production of 64-layer 3D TLC NAND chips starting September 2019. The company is skipping the 96-layer generation and moving directly to 128 layers.