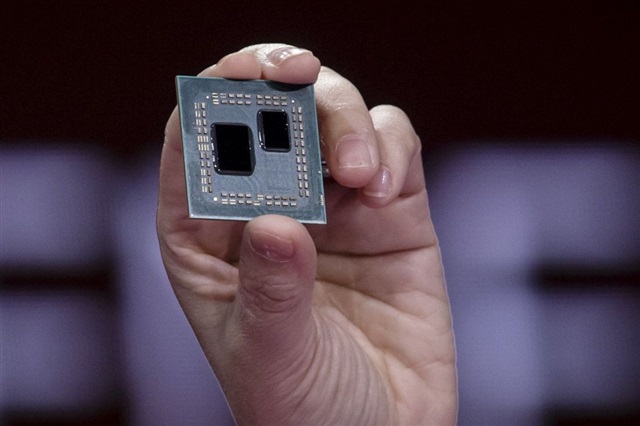

As automotive computing platforms increasingly demand higher performance, longer lifespans, and near-zero defect rates, chip architecture faces the challenge of balancing system reliability with cost efficiency under stringent automotive standards. Chiplets are emerging as a pivotal pathway to meet these requirements.

In an exclusive interview with Debendra Das Sharma, Intel Senior Fellow and chair of the Universal Chiplet Interconnect Express (UCIe) Consortium, Jessie Lin, senior analyst at DIGITIMES Research, discussed how UCIe 1.1 introduces enhanced features tailored for automotive applications. The new specification offers packaging options across different performance tiers and cost brackets, enabling automakers to strike an optimal balance between efficiency and affordability.

DIGITIMES breaks down the enhancements across four key dimensions: preventive monitoring, in-operation health diagnostics and self-repair, cost-optimized packaging, and cross-vendor interoperability.

Preventive Monitoring

UCIe 1.1 introduces a pre-check mechanism that tests inter-chip communication channels before data transmission begins. Similar to running a trial lap on a highway before full operation, the system sends a test signal to validate the stability and integrity of the connection.

If signal quality deteriorates during prolonged use, the system can retest and fine-tune the connection, reinforcing long-term reliability for automotive systems that are expected to run continuously with minimal maintenance.

Real-time health checks and self-healing

The new standard also adds real-time monitoring. During operation, UCIe 1.1 continuously assesses the condition of each data channel and logs anomalies. If a fault threatens stability, the system automatically isolates the compromised lane, activates a backup route, or recalibrates parameters such as signal strength and timing.

This self-healing capability minimizes unplanned downtime and reduces costly maintenance, meeting the automotive sector's demand for functional safety.

Packaging flexibility to optimize costs

To make Chiplets easier to integrate into cost-sensitive vehicles, UCIe 1.1 expands packaging flexibility. The update introduces new bump map layouts and data-lane configurations, giving designers more room to balance chip size, power efficiency, and manufacturing costs.

Das Sharma explained that the standard now clearly distinguishes between 2D, 2.5D, and 3D packaging. Automakers can match the option to their needs: 2D for budget-conscious applications, and 2.5D or 3D when higher bandwidth and better power efficiency are critical, such as in AI processors for Level 3 and above autonomous driving or advanced cockpit systems. This tiered approach ensures carmakers aren't forced into costly high-end packaging across the board, while still covering everything from short- to long-distance data transmission.

Cross-vendor interoperability and unified testing

UCIe 1.1 strengthens its compliance and testing framework to ensure chips from different vendors can interoperate seamlessly. The standard defines uniform communication protocols, error-handling rules, and verification procedures, lowering integration risks.

By aligning pre-production testing across the industry, the update enables plug-and-play compatibility, shortening development cycles and accelerating time-to-market.

Laying the groundwork for automotive chiplet adoption

Through pre-transmission validation, continuous health monitoring, real-time fault recovery, cost-conscious packaging, and strengthened interoperability, UCIe 1.1 directly addresses the automotive industry's stringent demands for zero defects, functional safety, and cost efficiency.

These enhancements establish a solid technical foundation for Chiplets to achieve wider deployment in next-generation automotive systems.

Article translated by Sherri Wang and edited by Jack Wu