Semiconductor industry research firm TechInsights said it has found that Samsung's 3nm GAA (gate-all-around) process has been incorporated into the crypto miner ASIC (Whatsminer M56S++) from a Chinese manufacturer, MicroBT.

In a Disruptive Technology Event Brief exclusively provided to DIGITIMES Asia, TechInsights points out that the significance of this development lies in the commercial utilization of GAA technology, which facilitates the scaling of transistors to 2nm and beyond. "This development is crucial because it has the potential to enhance performance, improve energy efficiency, keep up with Moore's Law, and enable advanced applications," said TechInsights, identifying the MicroBT ASIC chip the first commercialized product using GAA technology in the industry.

But this would also reveal that Samsung is the foundry for MicroBT, using the 3nm GAA process. DIGITIMES Research semiconductor analyst Eric Chen pointed out that Samsung indeed has started producing chips using the 3nm GAA process, but the capacity is still small. "Getting revenues from shipment can be defined as 'commercialization', but ASIC is a relatively simple kind of chip to produce, in terms of architecture."

DIGITIMES analyst John Wang highlighted the fact that the yield of Samsung's 3nm GAA process is still low, so it will try to get as many customers as possible to help train its processes and improve the yield. It is understandable why they would do business with a Chinese customer.

However, just like the SMIC 7nm process previously found by TechInsights in a MinerVa Bitcoin mining chip, analysts said the fact that the 3nm process is proved manufacturable does not necessarily mean it has achieved a satisfactory yield that can generate commercial value for the foundry at the current level.

Samsung claims its first-generation 3nm process could reduce power consumption by 45%, increase performance by 23%, and reduce chip area by 16% compared to 5nm technology, promising even more advances for future generations.

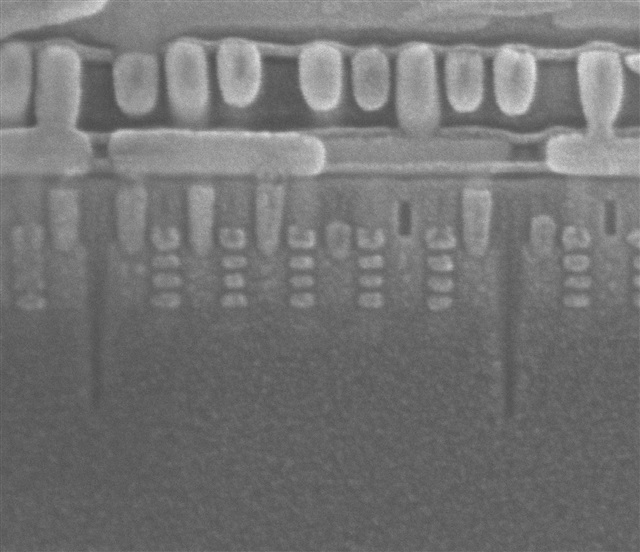

Credit: TechInsights; Whatsminer M56S++ SEM XS (Across gate, showing 3-level nanosheet)

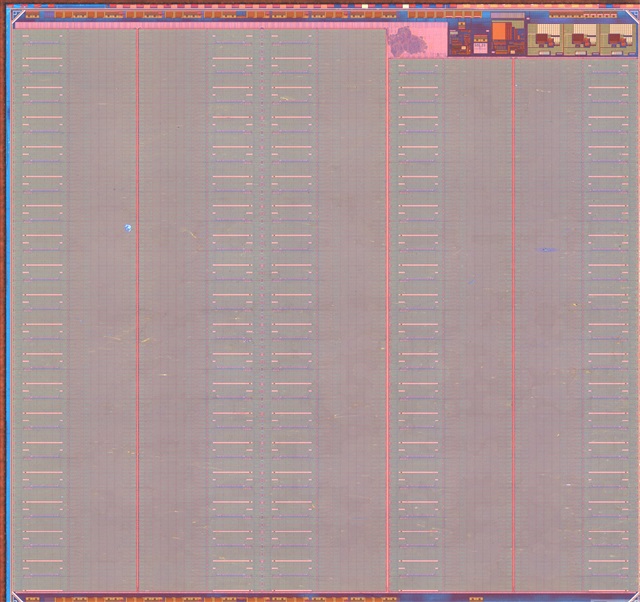

Credit: TechInsight; Whatsminer M56S++ die photo (back poly image)